PXI系统在工业领域得到了越来越多的应用,在使用PXI系统的同时,有必要对PXI系统本身特性尤其是PXI系统带宽有深入的了解。本文从纯硬件系统角度出发,对PXI系统带宽进行分析。首先分析PCI/PCI Express特点与性能,进而阐述PXI系统中Switch与Bridge的作用,并最终得到对PXI/PXI Express系统带宽的完整分析。对于PXI-8110与PXI-1042组成的系统,双向理论最大总机箱带宽为133MB/s,双向理论最大总系统带宽为133MB/s,双向理论最大总单槽带宽为133MB/s;对于PXIe-8133与PXIe-1075和PXIe8135与PXIe-1085组成的系统,单方向理论最大机箱带宽分别为4GB/s和12GB/s,单方向理论最大总系统带宽分别为4GB/s和8GB/s,单方向理论最大P2P带宽分别为1GB/s和4GB/s,单方向理论最大单槽带宽分别为1GB/s和4GB/s。

1. Introduction

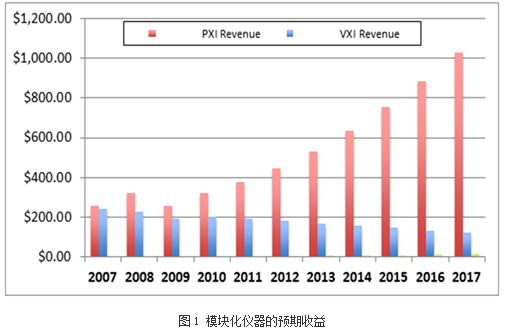

PXI(PCI eXtension for Instrumentation)系统是NationalInstruments最初在1997年提出的模块化仪器平台,并由PXISA(PXI System Alliance)推动PXI系统的发展,在2005年完成发布了PXIExpress系统标准。在2009年PXISA宣布超过100,000台PXI系统被部署,整个PXI市场有望在2017超过1,000,000,000美元。

National Instruments在申请的专利中,申明了通过扩展基于通道的交换结构,以便提供仪器信号功能的仪器系统。在这样的系统中,有用于传输数据的总线,以及实现仪器信号功能的仪器信号线。仪器信号线包括本地总线、触发总线和星形触发总线,但仪器信号线仅仅传递定时同步信号,故在本文中仅通过阐述传输数据总线来介绍PXI系统理论上的最大带宽。

PXI/PXIe系统采用PCI/PCI Express总线传递数据,所以在接下来的部分中,首先简要介绍PCI/PCIExpress总线,之后阐述利用PCI/PCI Express总线传输数据的PXI/PXIe系统带宽。

PCI(Peripheral Componet Interconnect)总线是Intel在1993提出的计算机本地总线,并由PCI-SIG(Peripheral Component Interconnect Special Interest Group)负责标准的制定。

PCI总线的数据采用并行传输,比特位宽为32位或64位,常用为32位,时钟速率为33MHz或者66MHz,常用为33MHz。对于33MHz的32位PCI总线来说,传输容量为133MByte/s。

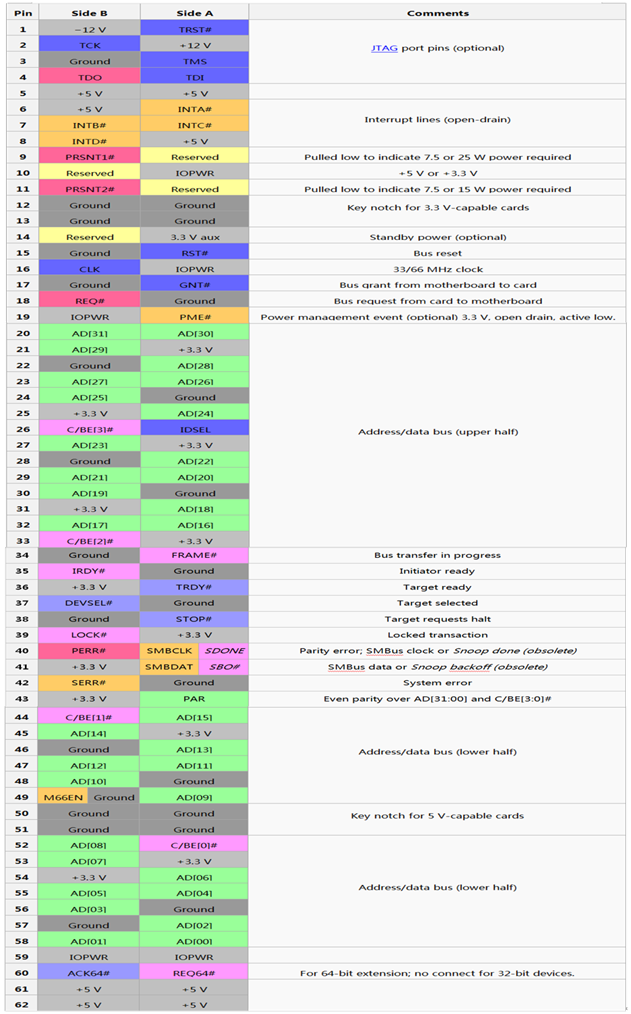

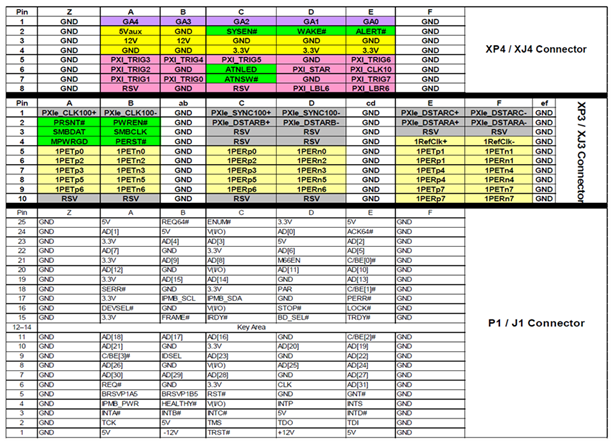

PCI总线的连接器针脚如表1所示,其中AD[00-31]为PCI地址/数据总线,为PCI中地址和数据传输所共用。

PCI总线上的设备并行接入到总线上,每个设备共享总线带宽,同一时刻只能有一个通信任务处于执行中,总线上设备占用总线带宽需要通过请求/授权协议进行申请,并且发送与接收共用相同总线。所以33MHz的32位PCI系统的传输容量133MB/s仅仅是理论上的最大双向总带宽,当总线上有多个设备的时候,平均到每个设备的实际带宽会明显下降。除此之外,由于PCI总线采用并行传输方式,当时钟速率升高时,多条传输线信号间同步很难保证,所以PCI总线的时钟速率难以显著提高,这也限制了总线的传输带宽。

PCI系统传输带宽的限制导致它无法满足最新诸如高速显卡等应用的需要,所以PCI-SIG在之后制定了PCI Express总线标准。

针对于越来越高的总线传输速度要求,PCI-SIG制定了PCI Expess总线标准。

PCI Express总线采用串行数据传输方式,避免了PCI总线并行方式带来的时钟速率无法显著提高的问题,数据传输速率可以很高。同时PCIExpress总线采用端到端连接方式,也就意味着传输链路并非多个设备共享,而是专属的传输链路。

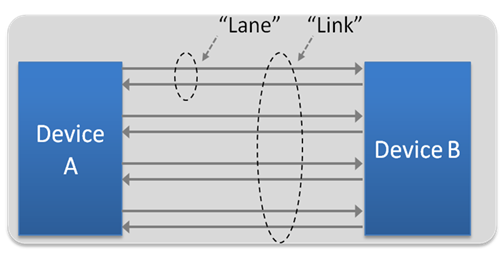

如图2所示,设备间互联的Link由若干个Lane组成,图2中的Link就由4个Lane组成,可以表示为×4Link。任何一个Lane包含两个差分信号对,一个差分对用于发送数据,另一个用于接收数据,也就是说一个Lane会包含4个信号线。这种结构可以全双工的同时发送与接收信号。

图2 PCI Express Link & Lane

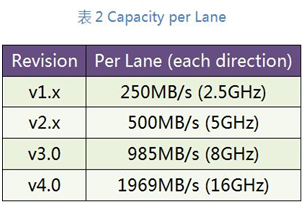

PCI Express Gen 1版本规定时钟速率为2.5GHz,同时采用8b/10b编码机制,所以每条Lane单方向传输数据的最大速率为250MB/s。PCI Express Gen 2版本将时钟速率增大为5GHz,编码方式不变,所以每条Lane单方向传输数据的最大速率增大为500MB/s。PCI Express Gen 3版本进一步将时钟速率提升为8GHz,同时采用128b/130b编码机制降低冗余编码开销。PCI-SIG正在积极制定新一代PCI Express Gen 4版本标准,以便传输速率再上新的台阶。目前PCIExpress Gen 1和Gen 2版本在NationalInstruments的PXIe系统中均得到应用,不同版本PCIExpress协议中,每条Lane单方向传输速率如表2所示。

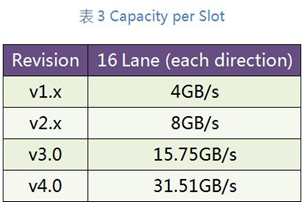

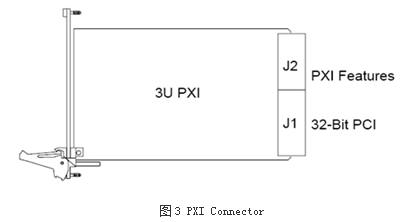

每条Link可以包含多条Lane(×1,×2,×4,×8,×16),最大为×16。每条Link中Lane的增加,可以整倍数的提升Link单向传输数据速率,如表3所示。

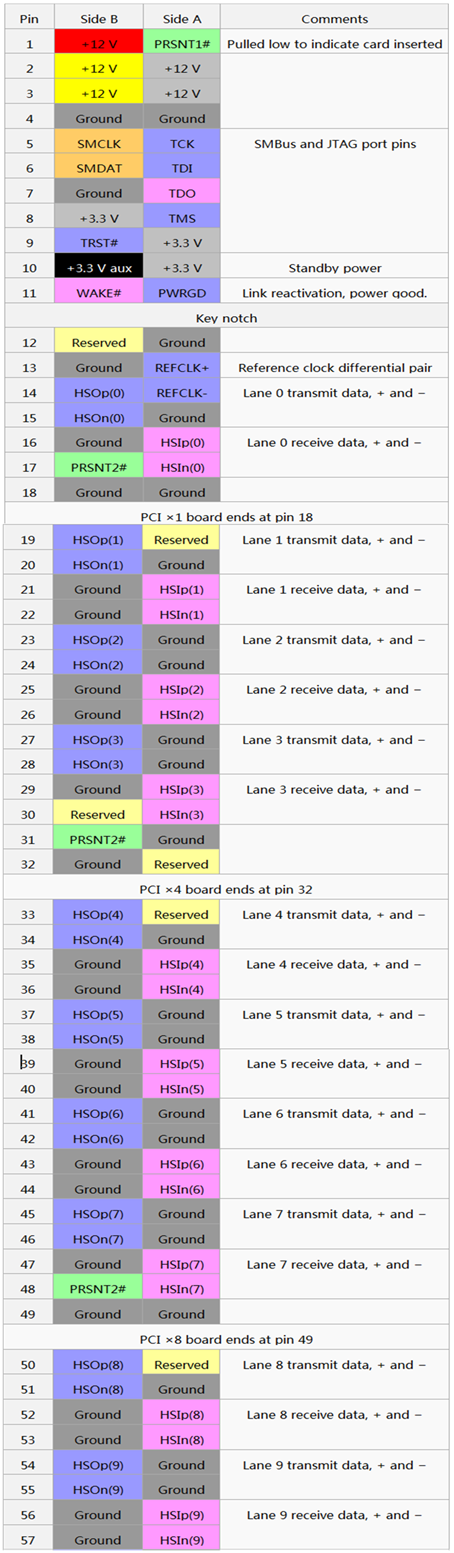

PCI Express的连接器针脚如表4所示。PCI Express采用串行通信方式,相比于PCI并行传输方式避免了多条传输线同步问题造成的传输速率无法显著提升的问题,只包含单条Lane的×1 Link可以达到250MB/s的传输速率,已经大于PCI所能提供的最大133MB/s传输速率,传输速率明显提升的同时插槽尺寸可以显著降低。此外PCI Express采用差分信号传输方式,可以有效消除共模干扰对信号的影响。

表4 PCI Express ×16 Connector Pinout

PXI/PXIe系统采用PCI/PCI Express总线传输数据,在本节中结合National Instruments推出的典型硬件产品(PXI-8110+PXI-1042/PXIe-8133+PXIe-1075/PXIe8135+PXIe-1085)对PXI/PXIe系统进行介绍。

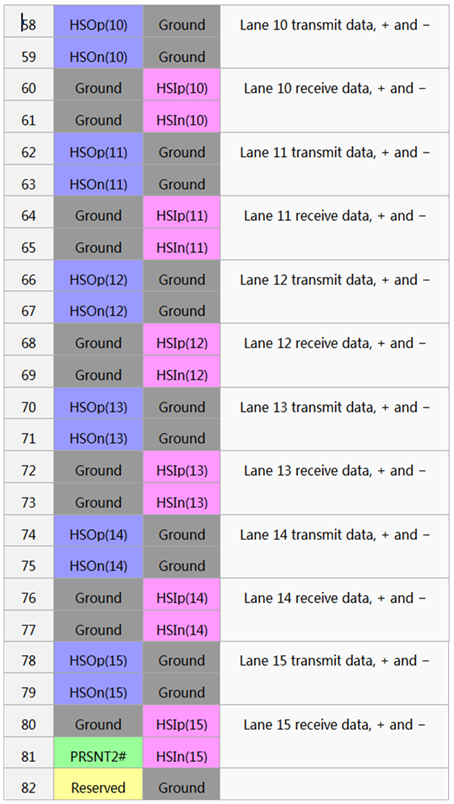

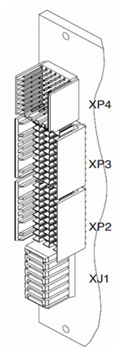

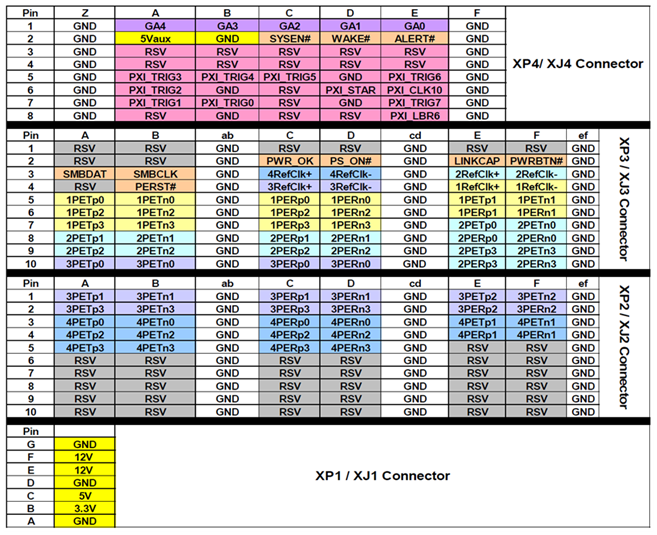

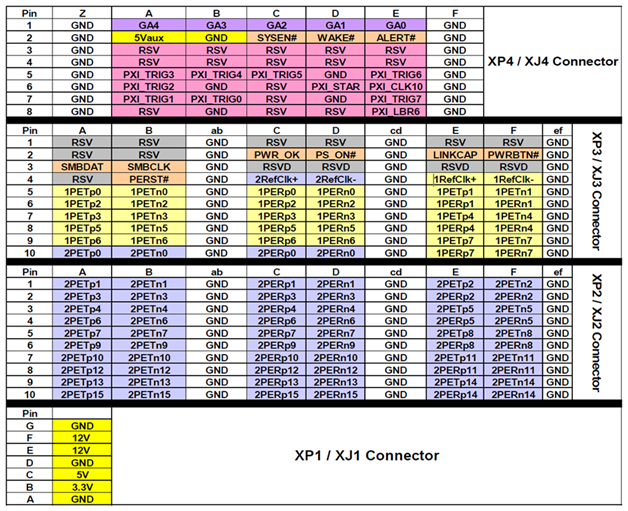

PXI系统采用PCI总线标准传输数据,并增加专用仪器信号线。在标准PXI系统中,功能板卡按需插入机箱中的通用Slot中。PXI系统中使用的Connector与Compact PCI相同,如图3所示。PXI系统Connector的Pinout是基于CompactPCI并添加仪器信号线得到的,Connector中J1与J2部分中Pinout情况如表5和表6所示。J1部分的Pinout就完全包含32bit PCI总线所需所有信号线,而J2部分一方面包含实现64bit PCI总线的高32bit数据位,同时也包括本地总线、触发总线、星形触发总线和参考时钟这些PXI系统添加的仪器信号线。

表5 J1 Connector Pinout

表6 J2 Connector Pinout

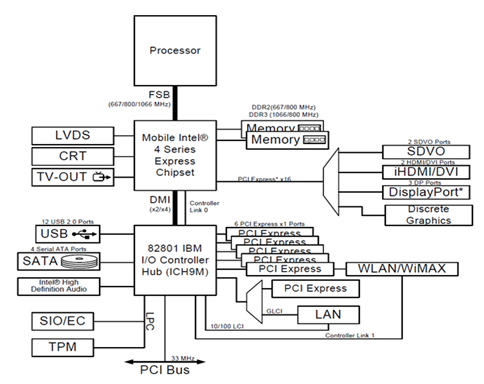

PXI-8110控制器硬件采用Mobile Intel GM45 Express Chipset并利用Intel 82801 Controller Hub来控制PCI总线连接,如图4和图5所示。

图4 Mobile Intel GM45 Express Chipset

图5 Intel 82801

PXI系统中的板卡插入机箱后,与PC中PCI总线板卡传输数据方式相同,共享PCI总线带宽,所以在32bit的33MHz时钟速率设备中,PXI系统拥有与PCI总线相同的133MB/s最大传输速率。总线上的设备平等共享PCI总线带宽,所以当功能板卡与控制器板卡传输数据,具有133MB/s最大传输速率,当总线上同时传输数据的设备数目增大时,平摊到每个设备的带宽会相应减小。

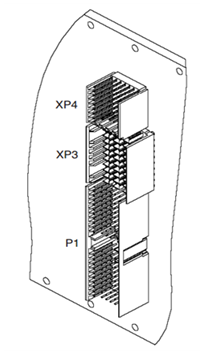

PXIe系统采用PCI Express总线传输数据,同时依然具有仪器信号线。PXIe系统Connector采用Compact PCI Express相同的Connector。相比于基于PCI总线的PXI系统,PXIe系统基于PCIExpress总线,数据传输采用差分信号对,所以板卡Connector有所不同,如图6和图7所示。

图6 3U PXI Express System Slot

图7 3U PXI Express Hybrid Peripheral Slot

混合插槽Connector的Pinout如图8所示,J1 Connector提供完整32bitPCI总线所需引脚,XP3 Connector提供一条×8PCI Express Link所需的引脚,而XP4 Connector跟PXI系统中Connector此位置引脚基本相同,只是本地总线缩减为只剩PXI_LBL6、PXI_LBR6这一对。

图8 Hybrid Peripheral Slot Pin Assignments

系统插槽比较特殊,可以有两种Link Configuration,分为4 Link Configuration和2 Link Configuration,Connector Pinout分别如图9和图10所示。从图中可以看到,4 Link Configuration可以提供四条×4 PCI Express Link,而2 Link Configuration可以提供一条×8 PCI Express Link和一条×16 PCI Express Link。

图9 Pin Assignments for 4 Link Operation

图10 Pin Assignments for 2 Link Operation

从Pinout可以看到,所有XP2和XP3 Connector中信号传输采用差分信号对,差分对与差分对之间有特殊形状GND引脚分割,可以满足高速数字信号的电磁兼容(EMC)和信号完整性(SI)要求。

了解PXIe系统Connector中Pinout情况对后续理解PXIe系统传输数据带宽有很重要的意义。

将相同类型网络连接在一起的器件称为Switch,而将不同类型网络连接在一起的器件称为Bridge。Switch与Bridge器件在PXIe系统中得到重要应用并直接影响PXIe系统带宽,所以在本小节中以PLX Technology公司产品为例简要介绍Switch与Bridge器件功能,下一小节介绍其在PXIe系统中应用。

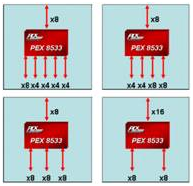

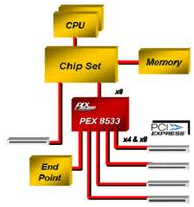

PLX Technology公司PEX 8533 PCIe Switch芯片和PEX 8112 PCIe-PCIBridge芯片得到了广泛的应用,其中PEX 8533 PCIe Switch芯片在PXIe-1075机箱中得到使用,从机箱背板上可以明显看出,如图11所示。

图11 PXIe-1075

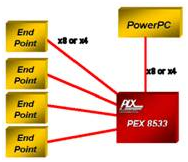

EX 8533 Switch有32条Lane,支持最多6个可配置端口。PEX 8533 Switch可以有多种端口配置方式,比如上行设置为×16 Port而下行为两条×8 Port,如图12所示。Switch芯片设置好的端口之间都可以实现双向数据的传输,这样的功能使得CPU可以通过Switch与多路PCIExpress扩展插槽进行通信,如图13所示,也可以让PXIExpress扩展之间直接实现P2P通信功能,如图14所示。

图12 Port Flexibility

图13 PCI Express扩展

图 14 Peer-to-Peer

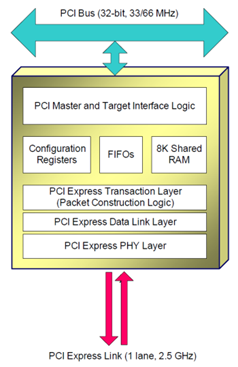

PEX 8112 PCIe-PCI Bridge可以实现×1 PCI Express Link与PCI总线的双向通信,由于一条PCI Express Lane的传输速率就已经大于整条PCI总线最大传输速率,所以Bridge芯片上只有一条×1 PCI Express Link,如图15所示。

图15 PEX 8112

当理解了PXIe系统组成单元的功能后,就不难理解PXIe系统的结构,本小节中结合PXIe-8133+PXIe-1075/PXIe8135+PXIe-1085进行介绍。

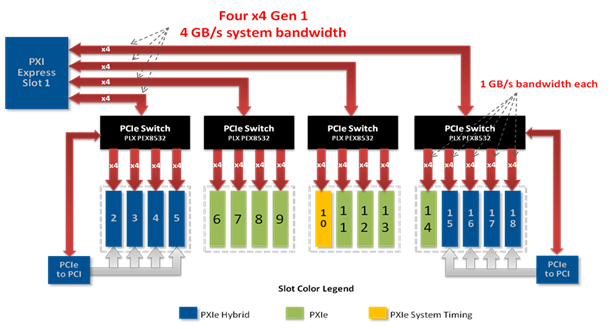

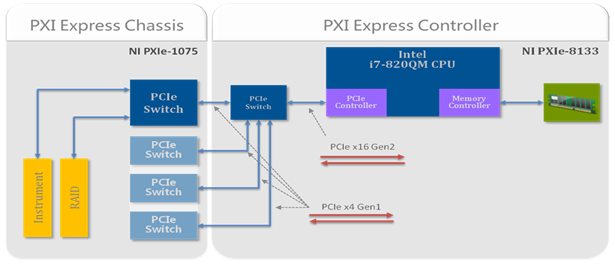

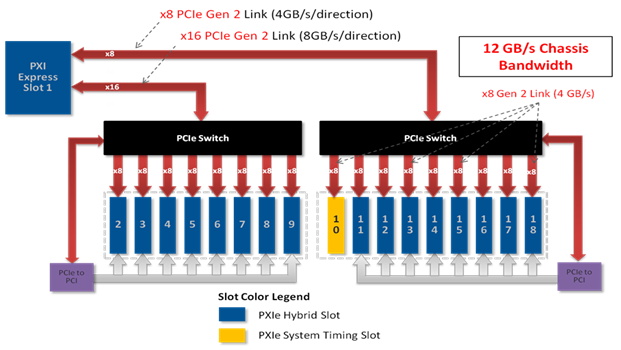

PXIe-1075系统架构如图16所示,机箱中每一个槽通过一条×4 PCI Express Gen 1 Link连接到Switch中,混合插槽中的PCI信号也可以通过Bridge间接与PCI Express Switch通信,同时每一个Switch都通过一条×4 PCI Express Gen 1 Link与控制器通信,总共4条这样的Link,这里Slot 1采用的是如图9所示的4 Link Operation。如图17所示,当Slot 1插入PXIe-8133控制器的时候,控制器上的Switch实现4条Link与CPU的通信,分别为四条×4 PCI Express Gen 1 Link,与CPU通信为一条×16 PCI Express Gen 2 Link。

所以纯PXIe-1075机箱理论上的单方向带宽为4GB/s,PXIe-8133与PXIe-1075构成的系统理论上的单方向系统带宽为4GB/s。

图16 PXIe-1075 System Architecture

图17 PXIe-1075 & PXIe-8133

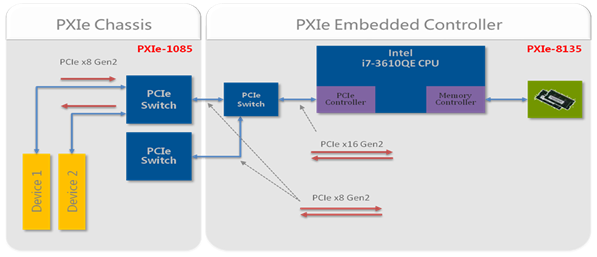

PXIe-1085系统架构如图18所示,机箱中每一个槽通过一条×8 PCI Express Gen 2 Link连接到Switch中,混合插槽中的PCI信号也可以通过Bridge间接与PCI Express Switch通信,同时一个Switch通过一条×8 PCI Express Gen 2 Link与控制器通信,另一个Switch通过一条×16 PCI Express Gen 2 Link与控制器通信,总共2条Link,这里Slot 1采用的是如图10所示的2 Link Operation。如图19所示,当Slot 1插入PXIe-8135控制器的时候,控制器上的Switch实现2条Link与CPU的通信,分别为两条条×8 PCI Express Gen 2 Link,与CPU通信为一条×16 PCI Express Gen 2 Link。

所以纯机箱PXIe-1085理论上的单方向带宽为12GB/s,PXIe-8135与PXIe-1085构成的系统理论上的单方向系统带宽为8GB/s。

图18 PXIe-1085 System Architecture

图19 PXIe8135 & PXIe-1085

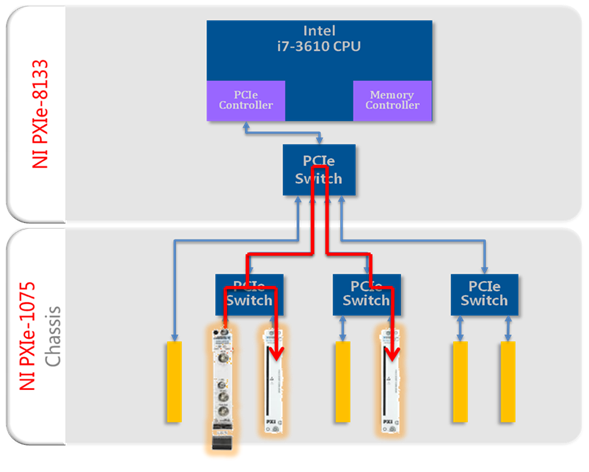

以PXIe-8133与PXIe-1075构成的系统为例介绍一下PXIe系统中P2P应用,如图20所示。当P2P连接的两块板卡与同一Switch相连时,可以直接通过该Switch完成P2P的应用,当这个条件不满足的时候,就需要借助控制器的Switch间接连接,理论上的单方向带宽为1GB/s。PXIe-8135与PXIe-1085构成的系统原理也一样,理论上的单方向带宽为4GB/s。

图20 Peer-to-Peer Streaming

PXI/PXIe系统带宽总结如表7所示。

表7 Theoretical Maximum Bandwidth

| Bandwidth | PXI | PXIe | |

PXI-8110+PXI-1042 (twodirections) | PXIe-8133+PXIe-1075 (perdirection) | PXIe8135+PXIe-1085 (perdirection) | |

| Chassis | 133MB/s | 4GB/s | 12GB/s |

| Total System | 133MB/s | 4GB/s | 8GB/s |

| P2P | N/A | 1GB/s | 4GB/s |

| Slot | 133MB/s | 1GB/s | 4GB/s |

PXI/PXIe系统采用PCI/PCI Express总线传输数据,并且随着通信协议的升级,通信速率得到显著提升。通过对PXI/PXIe系统纯硬件结构的分析,得出以下结论:对于PXI-8110与PXI-1042组成的系统,双向理论最大总机箱带宽为133MB/s,双向理论最大总系统带宽为133MB/s,双向理论最大总单槽带宽为133MB/s;对于PXIe-8133与PXIe-1075和PXIe8135与PXIe-1085组成的系统,单方向理论最大机箱带宽分别为4GB/s和12GB/s,单方向理论最大总系统带宽分别为4GB/s和8GB/s,单方向理论最大P2P带宽分别为1GB/s和4GB/s,单方向理论最大单槽带宽分别为1GB/s和4GB/s。

产品手册下载 服务热线:028-85291611 地址:成都市郫都区德源镇红旗大道南段427号(乐创孵化中心)217室 备案编号:蜀ICP备18004149号-1